#### High Speed Lateral Power Devices

#### Sameer Pendharkar

Analog Technology Development Texas Instruments Inc. Dallas, TX, USA

**Analog Tech. Development**

### Outline

- Integrated LDMOS

- Isolation Requirements

- Interconnect & Packaging

- Discrete lateral DMOS & Packaging

- Summary

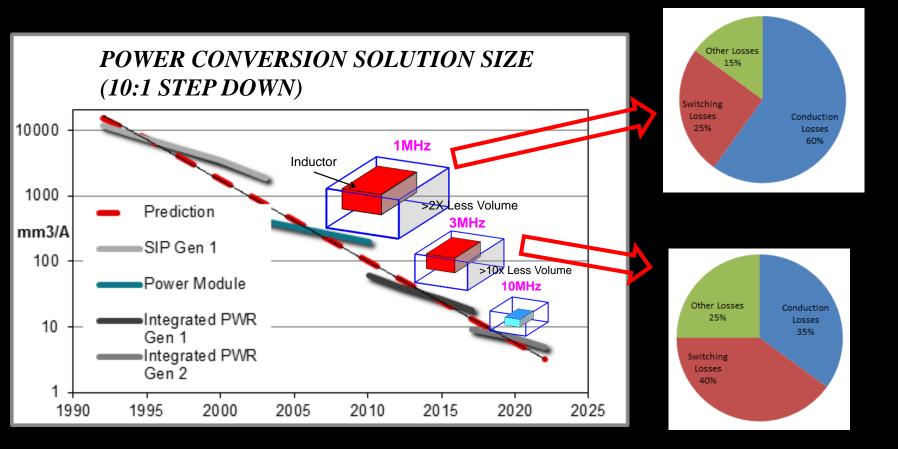

# High Frequency Switching

#### • End solution size is the primary driver

```

Analog Tech. Development

```

#### Key Power Device Drivers

- Rsp important → Key Si cost driver BUT

- R x Qtot(Qgd) & Qrr → Key performance drivers and system cost drivers ALSO NEED

- Reduced parasitics (gate loop and power loop L, CSI)

#### **Integration and Integrated LDMOS**

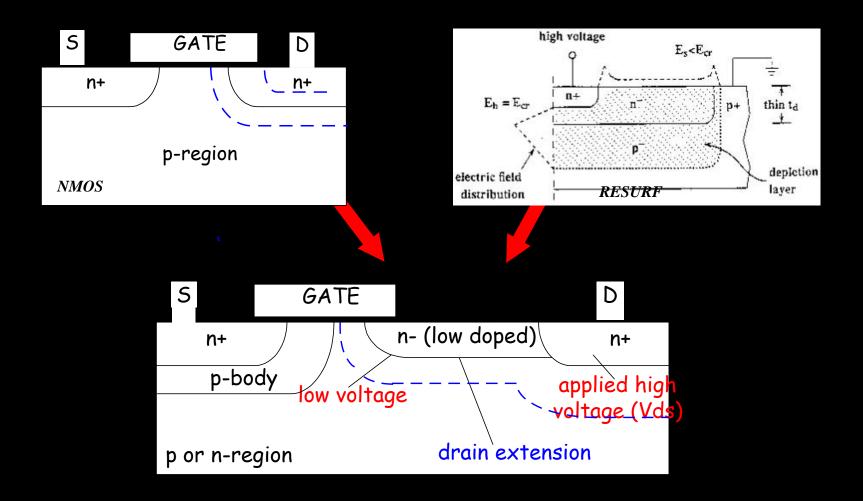

#### LDMOS

Analog Tech. Development

## LDMOS Benefit

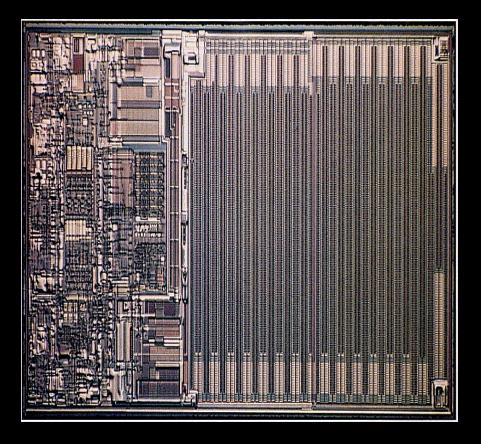

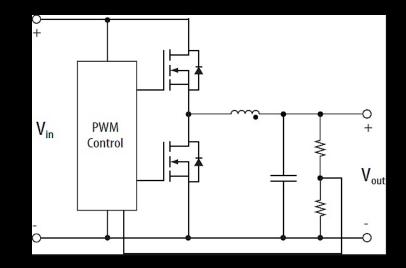

#### Synchronous Buck Converter – Monolithically Integrated Vin=12V, Vout=1.5V, I=10A

- Multi-voltage, Easy to Integrate

- Lowest Qg/Qtot for given Rdson monolithically integrated

- Low voltage integrated VDMOS not efficient due to significantly high Rsp

#### **Integrated Power Conversion**

High speed Synchronous Buck Converter

# • Monolithic integration helps reduce both gate loop and power loop inductance

Analog Tech. Development

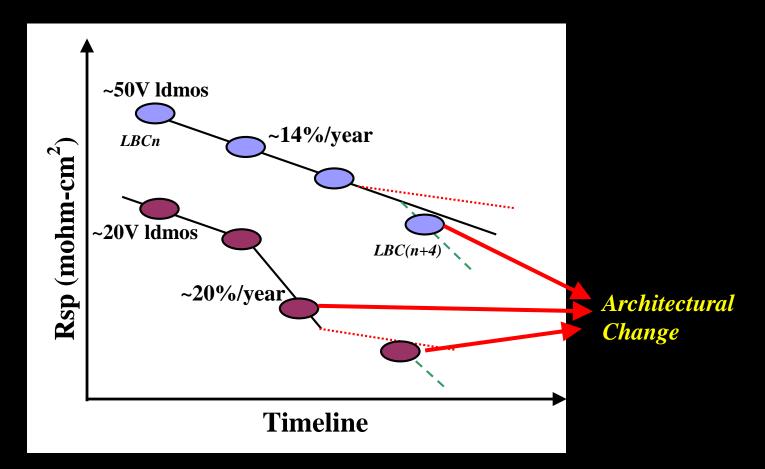

#### Integrated FET Scaling – Drives Technology

Integrated FET improvement at TI

about 25-30% node-on-node improvement

Analog Tech. Development

### Outline

- Integrated LDMOS

- Isolation Requirements

- Functionality

- Efficiency

- Interconnect & Packaging

- Discrete lateral DMOS & Packaging

- Summary

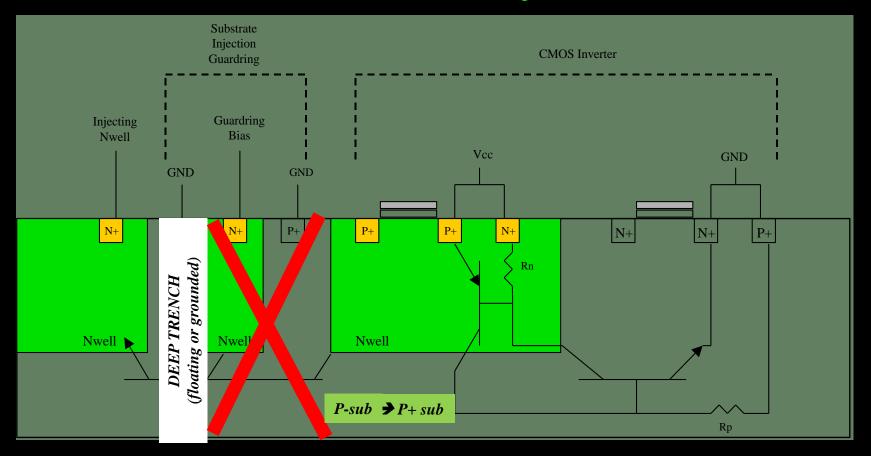

#### **Isolation - Functionality**

Protect circuitry from carrier injection

Diode recovery, Substrate bounce/noise

Analog Tech. Development

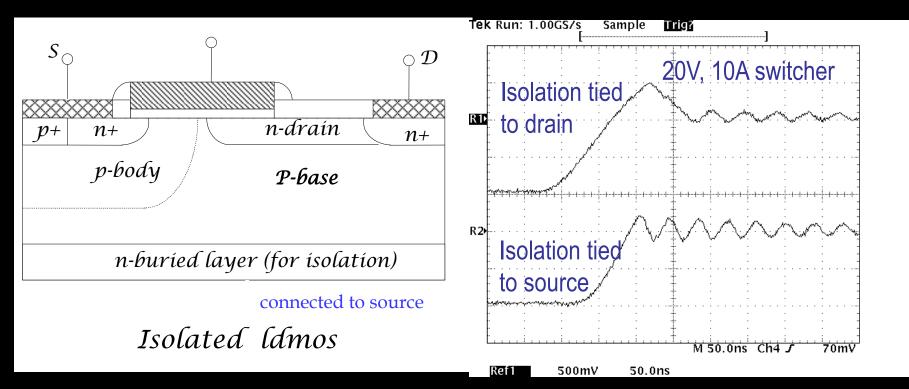

### Isolation – Efficiency Improvement

Integrated guard ring significantly reduces diode recovery loss → enables faster switching

Analog Tech. Development

### Outline

- Integrated LDMOS

- Isolation Requirements

- Interconnect & Packaging

- Electro migration

- Parasitic inductance

- Size and footprint

- Discrete lateral DMOS & Packaging

- Summary

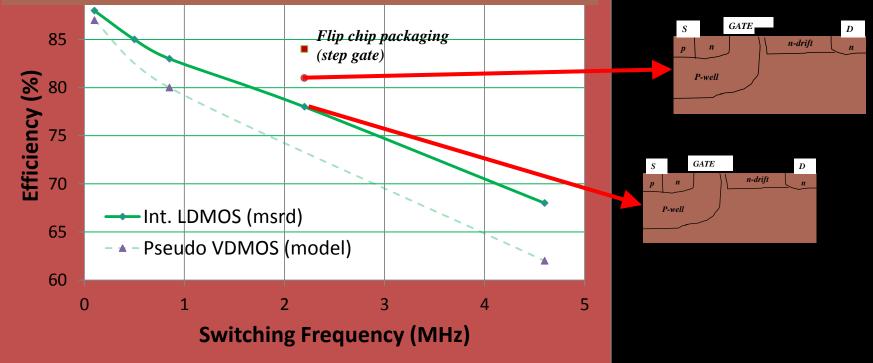

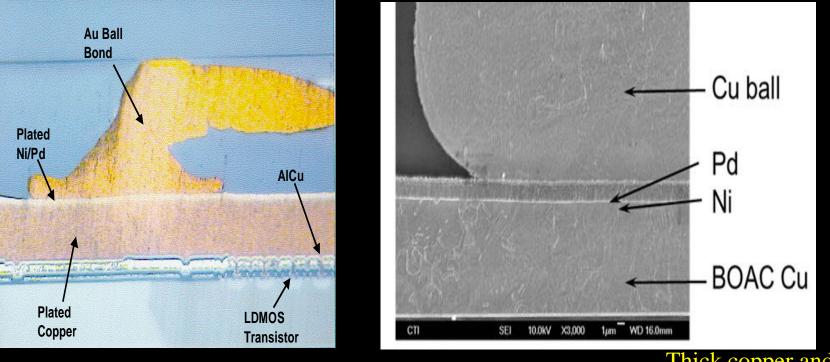

#### **Interconnect Optimization**

Thick copper and bonding technology

- Thick Copper allows direct bonding on top of active device delivers distributed current

- Enables flip chip package eliminating bondwires

Analog Tech. Development

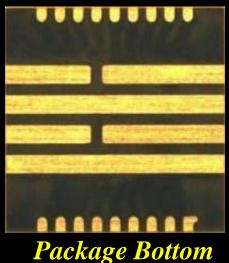

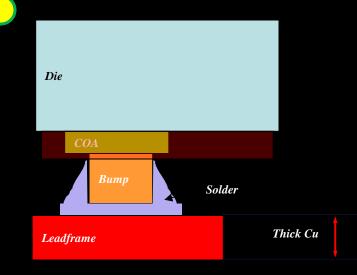

# HOTROD<sup>TM</sup> – Flip chip Package for Power

Flip-Chip **Eliminates Wire** Resistance & Wire Inductance

For Power Pins

#### Cu bumps on die

Technology for Innovators<sup>™</sup>

For Signal Pins

**Analog Tech. Development**

### Outline

- Integrated LDMOS

- Isolation Requirements

- Interconnect & Packaging

- Discrete lateral DMOS & Packaging

- Path towards higher current

- Reduced design cycle time

- Product flexibility

- Summary

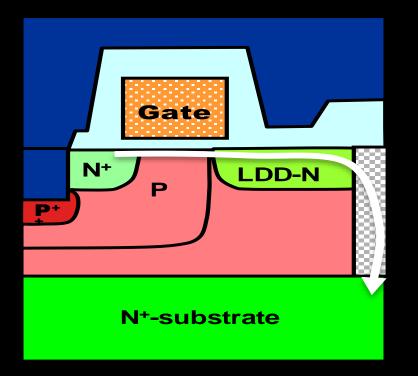

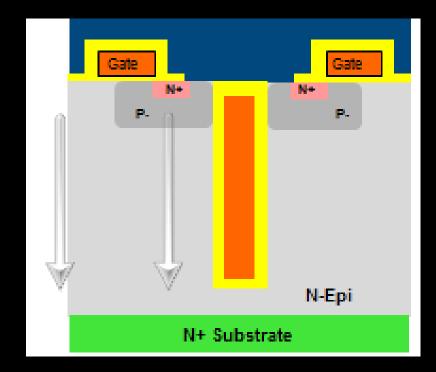

#### Discrete FET Technology

#### **NexFET<sup>TM</sup> LV Technology**

- LDMOS with Vertical Current Flow

- High density and low Rdson

- Low gate charge

#### **NexFET<sup>TM</sup> MV Technology**

- Planar gate for low gate charge

- SJ Trench for lower Rdson

- Low gate charge & fast switching

#### Analog Tech. Development

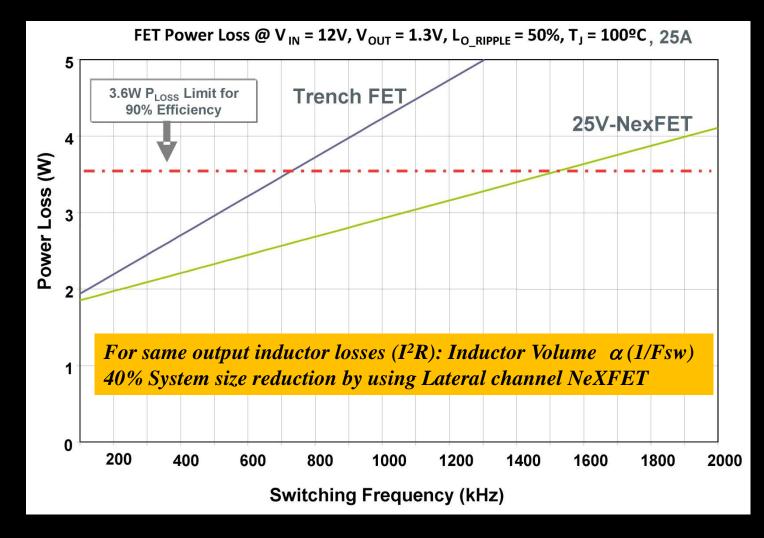

# Power Loss vs. Frequency for Trench DMOS and NexFET

Analog Tech. Development

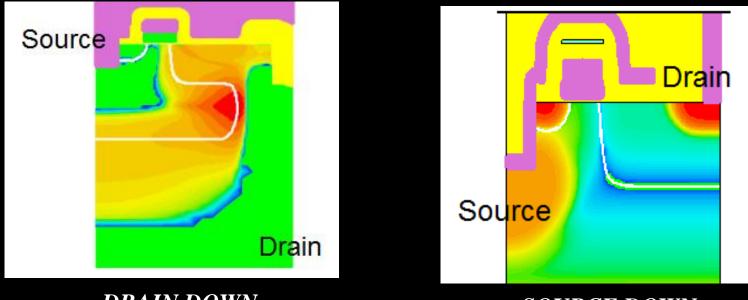

### "Lateral" Discrete FET Flexibility

DRAIN DOWN

SOURCE DOWN

- Same architecture allows both "drain down" & "source down" structures

- Accomodates functional integration

Gate clamp, Gate segmentation, slew control

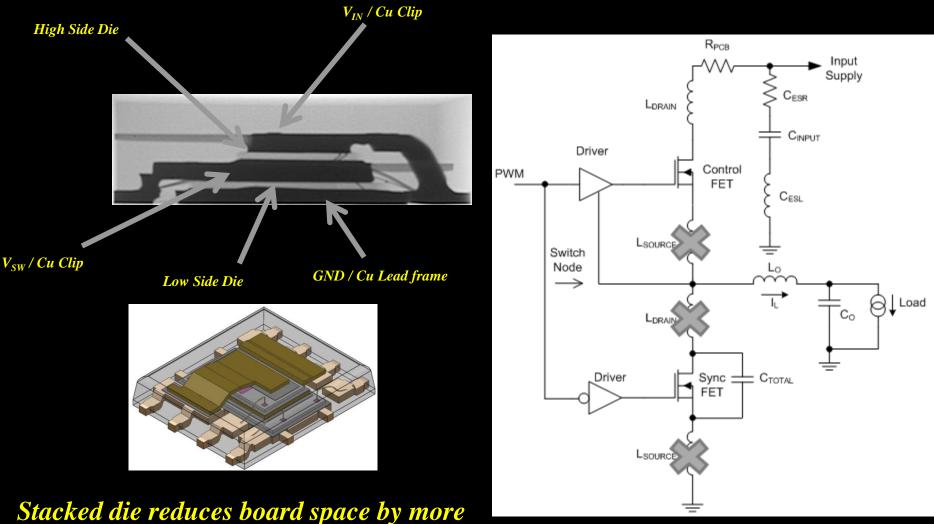

### Stacked Die Packaging – Power Block

Stacked die reduces board space by more than 50%

#### Analog Tech. Development

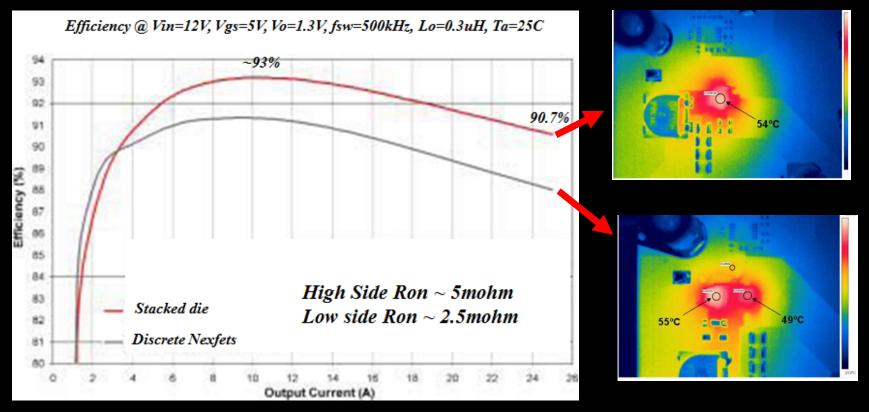

## Power Block – Efficiency Improvement

- About 20% reduction in losses with stacked die

- Similar die temperature/thermal performance

#### Summary

- Power conversion switching frequency increasing to enable footprint reduction

- Switching losses and diode losses more critical

- Lateral power DMOS structure ideally suited

*Can be implemented as integrated or discrete*

- Lower gate and power loop as well as package inductances while maintaining high current interconnect

- *Monolithic for low/mid current flip chip*

- Stacked die for high current – Cu clip

#### THANK YOU

Analog Tech. Development